利用ORAN IP的例子工程來做仿真

一個是新建Block Design,添加IP之后,通過運行Block Automation來產生一個....

Vitis視頻分析SDK構建自己的智能視頻分析解決方案

Vitis 視頻分析 SDK構建自己的智能視頻分析解決方案 Vitis 視頻分析 SDK 旨在 Xi....

賽靈思2021自適應計算挑戰賽技術講解分享會

賽靈思2021自適應計算挑戰賽自9月7日正式開賽以來,收到了來自全球各地區的FPGA軟硬件開發者們的....

基于PYNQ RFSoC框架的開源量子位控制器

費米實驗室,普林斯頓大學,芝加哥大學等科研機構聯合發表了基于PYNQ RFSoC框架的開源量子位控制....

賽靈思全新Test Drive試用體驗

賽靈思應用商店提供一個強大的平臺,其可使用一個簡單易用的安全數字版權管理 (DRM) 基礎架構來發布....

賽靈思2021自適應計算挑戰賽問題匯總

賽靈思2021自適應計算挑戰賽自9月7日正式開賽以來,收到了來自全球各地區的FPGA軟硬件開發者們的....

XILINX使用方法論設計無法連貫布線

本篇博文中的分析是根據真實客戶問題撰寫的,該客戶的 DFX 設計無法連貫布線,存在布線重疊。本篇博文....

硬件中存在DDR4校準后數據錯誤

本篇博文中的分析是根據真實客戶問題撰寫的,該客戶發現硬件中存在 DDR4 校準后數據錯誤,此問題顯示....

由于時鐘域交匯處理不當所導致罕見的比特翻轉

本篇博文中的分析是根據真實客戶問題撰寫的,該客戶發現在現場出現罕見的比特翻轉, 本篇博文旨在演示用于....

如何修復硬件中存在DDR4校準錯誤

本篇博文中的分析是根據真實客戶問題撰寫的,該客戶發現硬件中存在 DDR4 校準錯誤,不同板以及不同構....

HLS導出的.xo文件如何導入到Vitis里面

Q1 HLS導出的.xo文件如何導入到Vitis里面?需要把.xo文件解壓,然后把文件夾導入到Vit....

如何在訓練過程中正確地把數據輸入給模型

機器學習中一個常見問題是判定與數據交互的最佳方式。 在本文中,我們將提供一種高效方法,用于完成數據的....

如何使用ICAP在Spartan-3AN FPGA內運行多重啟動應用

(UG332) 即為《Spartan-3 系列配置用戶指南》 在此用戶指南中,并未涵蓋有關從 SPI....

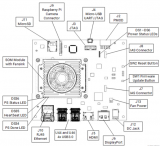

怎么在Vitis加速設計中為Kernel創建面積約束

本文來自賽靈思高級產品應用工程師 Hong Han Alveo系列開發板上的平臺其實是一個DFX設計....